# **Dietmar Tutsch**

Performance Analysis of Network Architectures

Performance Analysis of Network Architectures

Dietmar Tutsch

# Performance Analysis of Network Architectures

With 98 Figures and 12 Tables

Author

Dietmar Tutsch Institut für Technische Informatik und Mikroelektronik Technische Universität Berlin Einsteinufer 17 10587 Berlin Germany DietmarT@cs.tu-berlin.de

Library of Congress Control Number: 2006929315

ACM Computing Classification (1998): C.2, C.4, G.3, I.6

#### ISBN-10 3-540-34308-3 Springer Berlin Heidelberg New York ISBN-13 978-3-540-34308-0 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilm or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable for prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2006 Printed in Germany

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Typeset by the author Production: LE-TEX Jelonek, Schmidt & Vöckler GbR, Leipzig Cover design: KünkelLopka Werbeagentur, Heidelberg

Printed on acid-free paper 45/3100/YL - 543210

# Preface

This monograph has only become possible due to broad support from many people. Without their work and ideas, the research presented would never have been as successful.

I would like to thank Prof. Günter Hommel for supervising my research and for his valuable comments and suggestions, which were very important for this work. Prof. Hommel has always been addressable for fruitful discussions. In addition, I am deeply grateful to Prof. Miroslaw Malek for his continuous support of my work. He has spent much time in meetings with me to direct my interest to several new topics.

This monograph also represents the author's habilitation thesis. Sincere thanks goes to all its reviewers, Prof. Hommel and Prof. Malek as well as Prof. Manfred Glesner and Prof. Peter Kropf. In addition, I am indebted to Prof. Hans-Ulrich Heiß and Prof. Thomas Sikora who joined the habilitation committee with Prof. Hommel and Prof. Malek. I appreciate their time and effort for supporting my work.

Furthermore, I am very grateful to Joachim Sokol for supporting my research on ubiquitous computing. I would also like to thank all my former and current colleagues for discussions and resulting ideas and concepts. Particularly, I am very grateful to Daniel Lüdtke and Marcus Brenner for our weekly meetings and discussions about our common work on network architectures. Sincere thanks also go to Eveline Homberg for drawing many figures of this monograph.

Finally, I am indebted to all those students of TU Berlin who have been involved in my research, especially to Daniel Benecke, Rainer Holl-Biniasz, Matthias Kühm, and Arvid Walter, who implemented many components in our software tools and did excellent work.

Technische Universität Berlin,

Dietmar Tutsch June 2006

# Contents

| 1 | Intr | oductio | on                                      | 1  |

|---|------|---------|-----------------------------------------|----|

|   | 1.1  | Motiva  | tion                                    | 2  |

|   | 1.2  | Contril | bution                                  | 3  |

|   | 1.3  | Related | 1 Work                                  | 4  |

|   | 1.4  | Term I  | Definitions                             | 5  |

|   |      | 1.4.1   | Models and Performance Evaluation       | 5  |

|   |      | 1.4.2   | Parallel System Architecture            | 6  |

|   |      | 1.4.3   | Distributed System Architecture         | 7  |

|   |      | 1.4.4   | Network Architecture                    | 8  |

| 2 | Cha  | racteri | stics of Network Architectures          | 11 |

|   | 2.1  |         | ing Techniques                          | 11 |

|   |      |         | Circuit Switching                       | 11 |

|   |      |         | Packet Switching                        | 12 |

|   | 2.2  |         | Patterns                                | 14 |

|   |      |         | Distribution in Space                   | 14 |

|   |      |         | Distribution in Time                    | 15 |

|   | 2.3  | Wired   | Network Architectures                   | 21 |

|   |      | 2.3.1   | Basic Classifications                   | 22 |

|   |      | 2.3.2   | Bus                                     | 23 |

|   |      | 2.3.3   | Mesh                                    | 23 |

|   |      | 2.3.4   | Torus                                   | 25 |

|   |      | 2.3.5   | Ring                                    | 25 |

|   |      | 2.3.6   | Star                                    | 26 |

|   |      | 2.3.7   | Tree                                    | 27 |

|   |      | 2.3.8   | Hypercube                               | 27 |

|   |      | 2.3.9   | Crossbar                                | 28 |

|   |      | 2.3.10  | Multistage Interconnection Network      | 30 |

|   |      |         | Switching Fabric                        |    |

|   |      |         | Dynamic Networks versus Static Networks |    |

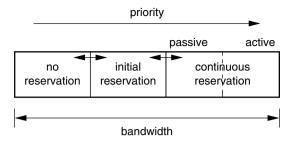

|   | 2.4  | Wireles | ss Network Architectures                | 47 |

|   |      |         |                                         |    |

|          |                        | 2.4.1          | Basics in Wireless Transmission              |       | 48  |  |

|----------|------------------------|----------------|----------------------------------------------|-------|-----|--|

|          |                        | 2.4.2          | Cellular Networks                            |       | 52  |  |

|          |                        | 2.4.3          | Ad-hoc Networks                              |       | 54  |  |

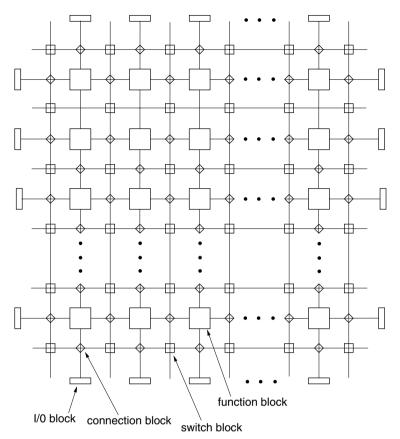

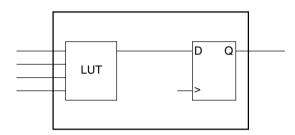

|          | 2.5                    | Netwo          | ork-on-Chip Architectures                    |       | 55  |  |

|          |                        | 2.5.1          | Origin and Use                               |       | 56  |  |

|          |                        | 2.5.2          | Particular Characteristics                   |       | 58  |  |

|          |                        | 2.5.3          | Topologies                                   |       | 60  |  |

|          | 2.6                    | Netwo          | ork Reconfiguration                          |       | 62  |  |

|          |                        | 2.6.1          | Reconfiguration Types and Levels             |       | 63  |  |

|          |                        | 2.6.2          | Dynamic Reconfiguration                      |       | 64  |  |

|          |                        | 2.6.3          | Reconfigurable Hardware Architectures        |       | 67  |  |

| 3        | Performance Evaluation |                |                                              |       |     |  |

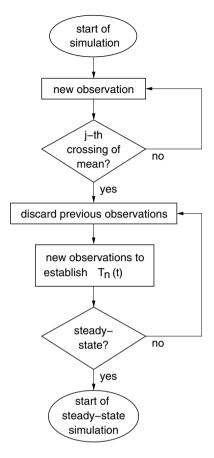

| 0        | 3.1                    |                | rical Simulation                             |       | 74  |  |

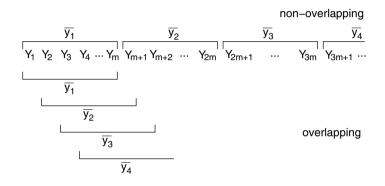

|          | 0.1                    | 3.1.1          | Statistics                                   |       | 75  |  |

|          |                        | 3.1.2          | Acceleration                                 |       | 82  |  |

|          | 3.2                    | ··             | v Chains                                     |       | 85  |  |

|          | 0.2                    | 3.2.1          | Markov Process                               |       | 86  |  |

|          |                        | 3.2.2          | Discrete Time Markov Chain                   |       | 86  |  |

|          |                        | 3.2.2          | Continuous Time Markov Chain                 |       | 90  |  |

|          |                        | 3.2.4          | Solution Methods                             |       | 93  |  |

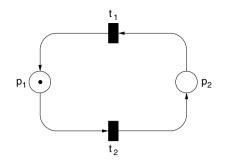

|          | 3.3                    |                | Nets                                         |       | 99  |  |

|          | 0.0                    | 3.3.1          | Basic Petri Nets                             |       | 99  |  |

|          |                        | 3.3.2          | Stochastic Petri Nets                        |       |     |  |

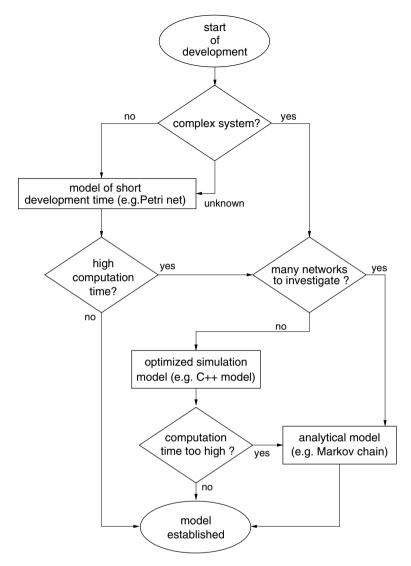

| 4        | Ма                     | dal En         | gineering                                    |       | 107 |  |

| 4        | 4.1                    |                | l Development                                |       |     |  |

|          | 4.1                    | 4.1.1          | Simulation Model                             |       |     |  |

|          |                        | 4.1.1          | Mathematical Model                           |       |     |  |

|          | 4.2                    |                | lexity Reduction                             |       |     |  |

|          | 4.2                    | 4.2.1          | Simulation                                   |       |     |  |

|          |                        | 4.2.1<br>4.2.2 | Mathematical Model                           |       |     |  |

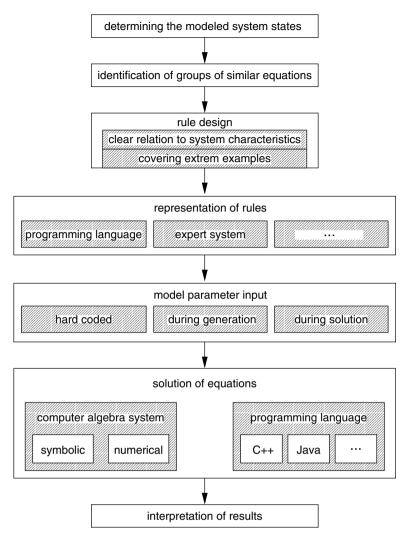

|          | 4.3                    |                | natic Model Generation                       |       |     |  |

|          | 4.0                    | 4.3.1          | Rule Design                                  |       |     |  |

|          |                        | 4.3.1          | Generating Systems of Equations              |       |     |  |

|          |                        | 4.3.2          | Generator Design                             |       |     |  |

|          |                        | 1.0.0          |                                              | ••••• | 101 |  |

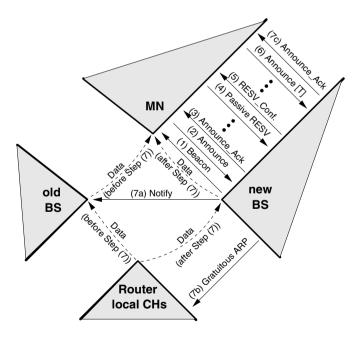

| <b>5</b> |                        | plicatio       | on: Cellular Network                         | ••••• | 133 |  |

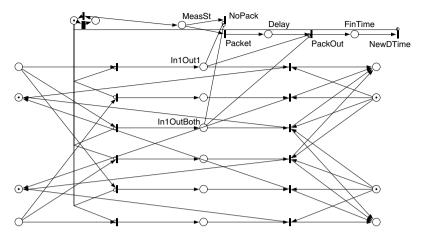

|          | 5.1                    |                | A Framework                                  |       |     |  |

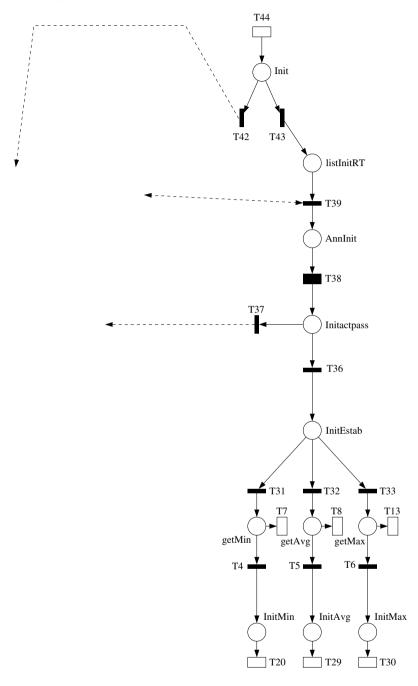

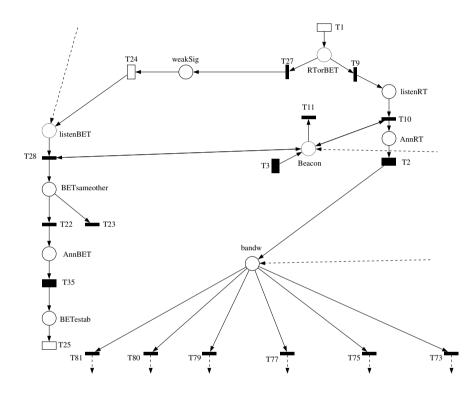

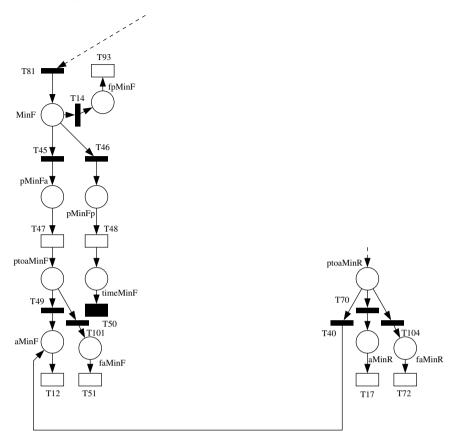

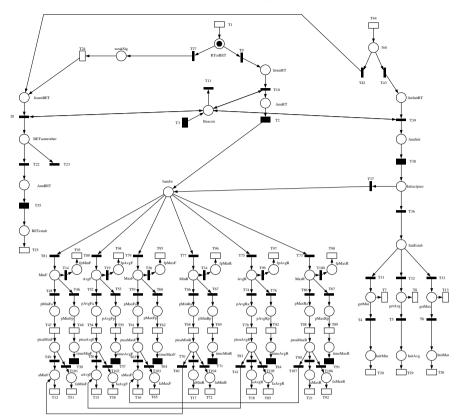

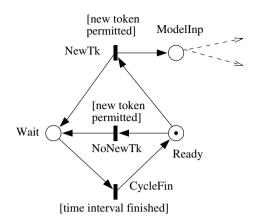

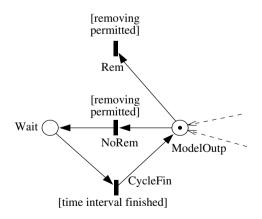

|          | 5.2                    |                | Net Model                                    |       |     |  |

|          |                        | 5.2.1          | Initialized Mobile Nodes                     |       |     |  |

|          |                        | 5.2.2          | Real-time Traffic                            |       |     |  |

|          |                        | 5.2.3          | Entire Model                                 |       |     |  |

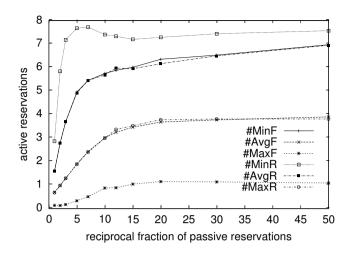

|          | 5.3                    |                | Engineering and Performance                  |       |     |  |

|          |                        | 5.3.1          | Model Development and Complexity Reduction . |       | 148 |  |

|     |       | 5.3.2    | Modeling Power                            | 148 |

|-----|-------|----------|-------------------------------------------|-----|

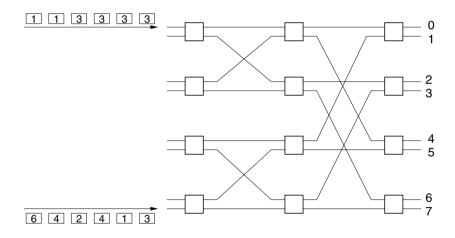

| 6   | Арг   | olicatio | n: Multistage Interconnection Network     | 153 |

|     | 6.1   |          | tion: Petri Nets                          |     |

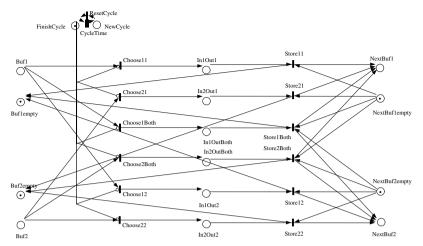

|     |       | 6.1.1    | Full Petri Net Model                      | 154 |

|     |       | 6.1.2    | Iterative Petri Net Model                 | 158 |

|     |       | 6.1.3    | Multicast Probabilities                   | 161 |

|     | 6.2   | Simula   | ation: <i>MINSimulate</i>                 | 165 |

|     |       | 6.2.1    | Simulator Engineering                     | 166 |

|     |       | 6.2.2    | Features                                  |     |

|     | 6.3   | Mathe    | matical Model: Complexity Reduction       | 172 |

|     |       | 6.3.1    | Symmetries                                |     |

|     |       | 6.3.2    | Multiple State Spaces                     | 184 |

|     |       | 6.3.3    | Fixed Point Iteration                     | 189 |

|     | 6.4   | Mathe    | matical Model: Automatic Model Generation | 192 |

|     |       | 6.4.1    | Rule Design                               | 192 |

|     |       | 6.4.2    | Generating and Solving the Equations      | 209 |

|     |       | 6.4.3    | Changing the Model                        |     |

|     | 6.5   | Model    | Engineering and Performance               |     |

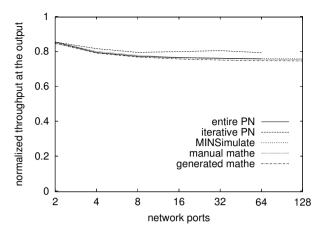

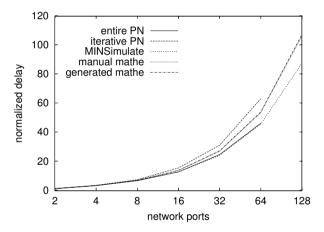

|     |       | 6.5.1    | Comparison of the Modeling Techniques     |     |

|     |       | 6.5.2    | Model Capabilities                        |     |

| 7   | Con   | cludin   | g Remarks                                 | 219 |

| Ref | feren | ces      |                                           | 223 |

| Ind | lex   |          |                                           | 239 |

# Introduction

Parallel and distributed computer systems are built to close the gap between high-performance demands in computing and the available computing power of stand-alone single processor machines. Choosing an appropriate network architecture to connect the parallel or distributed computer system plays an important role in the development process of the system. An ineligible network architecture may significantly delay the communication between the parallel or distributed components and decrease the system performance.

This book introduces the different kinds of network architectures. Wired architectures as well as wireless ones are taken into account. Various network topologies are presented, including their main components, the switches which realize the input-output connections in network nodes. The internal structure of networks and switches is exhaustively discussed. In addition, a new network topology is presented.

The advantages and drawbacks of the various switch structures and network topologies are described to work out their favored application areas. For instance, these areas depend on their related network traffic. Thus, the network traffic is also focused on in this book. The traffic is characterized by its distribution in time and space. Knowing the distribution in time is important to sufficiently dimension the network components, e.g., the buffer sizes. On the other hand, knowing the distribution in space helps choose an appropriate network topology supporting this distribution.

An important item in characterizing the advantages and drawbacks of switch and network architectures is comparing their performance. To improve this characterization by performance evaluation, a new method to determine network performance of parallel and distributed systems is derived in this book. Furthermore, guidelines and engineering techniques are given to rapidly establish models of the system in question, to reduce their complexity, and to solve them in a time-saving manner. These guidelines result in a systematization of the model development process and help set up appropriate models.

# 1.1 Motivation

To evaluate the performance of networks is a challenging task. Many parameters influence the performance of a particular network architecture. To determine its performance, three methods can be applied.

- 1. Measurement: The system hardware has to be set up to connect measurement devices.

- 2. Simulation: A software model of the system has to be set up, and simulation runs lead to the performance results.

- 3. Mathematical methods: Systems of equations have to be established to model the system in question. Performance is derived by solving these equations.

Measurement suffers from the huge drawback that the system must first be realized in hardware before any measurement can start. If it then turns out that the system does not fulfill the required performance, the architecture must be changed. Repetitively reconstructing it several times until the optimal architecture is found consumes much time and money. Thus, modeling with simulation or mathematical methods is the most appropriate technique. Nevertheless, measurement should not completely be excluded. Many systems are too complex to be determined by simulation or mathematical methods if detailed and accurate results are required. Then, measurement often turns out to be the only feasible solution. Furthermore, measurement also helps validate any results achieved by simulation or mathematical methods. Inaccuracies and errors in those models can be detected.

This book mainly focuses on simulation and mathematical methods. Features, strengths, and drawbacks related to simulation and mathematical methods are investigated. But before these techniques can be applied to evaluate parallel and distributed system architectures, models according to the methods must be derived.

Model development is a difficult task. Experience is needed, as well as creativity. Usually, no general rules can be given for model development. But guidelines can be presented from the experience acquired while establishing models. One should be aware that badly engineered models lead to timeconsuming performance evaluation, or they are not even able to produce any results due to their huge size and limited computer power and memory. Therefore, this book additionally introduces model engineering techniques related to the investigated performance evaluation methods.

Summarizing previous items, the following challenges emerge:

- Fast model development is desired. Guidelines of experienced developers may help in model set-up. These guidelines must be established.

- Models should be developed in such a way that they can be simulated or mathematically solved in a short time to produce results fast. Guidelines and model engineering techniques that lead to such models are required.

3

• Models should accurately represent the real-world system. Previously mentioned guidelines and engineering techniques should consider this.

The following chapters give some guidelines and model engineering techniques that fulfill the above issues and help in model development.

# 1.2 Contribution

This book focuses on the model engineering of network and switch architectures for parallel and distributed systems. Particularly, simulation models and mathematical models are of interest. The models are established to allow system performance evaluation. Examining the architecture implies coping with different network topologies, different buffer positions and sizes, different switch sizes, etc. Routing, protocols, and fault tolerance are not in the scope of this book.

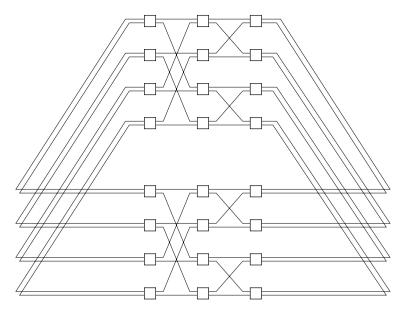

In Chap. 2, the characteristics of networks for parallel and distributed systems are described, including switching techniques, traffic patterns, and wired and wireless network architectures. With regard to traffic patterns, not only if the distribution in time taken into account, the distribution in space is also considered. Particularly, multicast distributions and the network topology support for multicast are examined. As a result of this research, a new wired network architecture was developed, and is presented in Sect. 2.3.10. This new architecture is called multilayer multistage interconnection network (MLMIN), and heavily increases network performance in the case of multicast traffic.

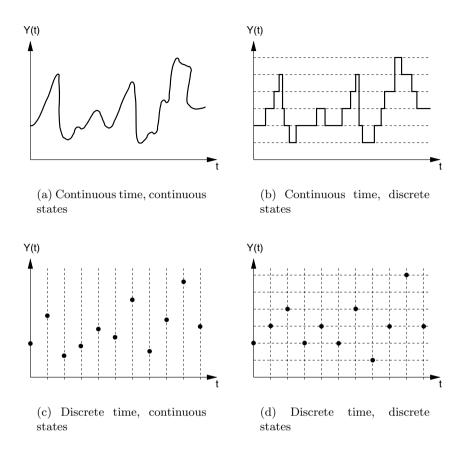

Methods for performance evaluation of parallel and distributed systems are discussed in Chap. 3. Simulation and mathematical methods are presented. Simulation refers to discrete event simulation only. Continuous simulation is not taken into account due to its drawbacks (see Sect. 3.1). With regard to mathematical methods, the focus is on Markov chains and Petri nets. Queuing theory suffers from its problems in modeling complex network topologies and is thus not considered here.

Establishing a simulation model or a mathematical model calls for some "feeling" of how to design an appropriate model. A model quickly becomes too large or too complex, resulting either in huge calculation times or, worse, in no solution at all. On the other hand, setting up a small model with low calculation times may consume much time during development. Furthermore, small models usually neglect too many details, and are thus too inaccurate.

In Chap. 4, some new guidelines for model development and complexity reduction are given. These guidelines evolved while establishing many models of communication networks to determine their performance.

The presented guidelines include a new concept of automatic model generation that gives a strategy for how to develop a generator for automatic model derivation. Of course, such a concept saves much development time. Two examples show how to apply the above concepts. A smaller example presented in Chap. 5 deals with a cellular network. It examines the handoff procedure of mobile nodes carrying real-time traffic. Due to the modest model size, a Petri net description sufficiently handles the system in question.

Unfortunately, this is not valid for the second example, which is dealt with in Chap. 6. Multistage interconnection networks are modeled to optimize their architecture. They are of common interest due to their use in parallel computers and in switches connecting distributed systems; their reconfiguration properties are also examined currently [124].

It turns out that this system is too large to be simply modeled by Petri nets. Other techniques like simulation and Markov chains are also applied and compared. The automatic model generation particularly accelerates model development, and is thus a good option in model establishment.

# 1.3 Related Work

Much research has been performed in investigating the performance of parallel and distributed systems, particularly in the area of communication networks connecting the nodes of such systems. Methods to evaluate the performance include Markov chains, queuing theory, Petri nets, and simulation (see Chap. 3). The most important publications are referenced in the following.

A broad theory about Markov chains is provided by many publications [4, 19, 44, 53, 54, 92, 95, 96, 199]. Especially, [19] does not introduce only Markov chains: The research groups of the authors also focus on queuing theory. Thus, this book also states the relation between Markov chains and queuing theory. Other publications introducing queuing theory are, for instance, [61, 72, 95, 96, 137, 199].

Some research groups which deal with Markov chains also apply Petri nets as a modeling method. Their publications and those of other authors describing Petri nets are, for instance, [36, 63, 75, 86, 118, 128, 144, 160, 165]. Finally, simulation methods are exhaustively treated in [9, 23, 57, 88, 107, 248].

Some publications particularly deal with the performance evaluation of multistage interconnection networks, which is one of the applications of this book. In the following, it is concentrated on research that was published during the last years. Older publications (but also newer ones) are cited in the chapters of this book to which they are related, where they are discussed in detail.

Group communication in circuit-switched multistage interconnection networks (MINs) is investigated in [242] by applying Markov chains. Markov chains are also used in [250] to compare MIN performance in the case of different buffering schemes. Hot-spot traffic performance in MINs is examined in [87]. [200] deals with multicast in Clos networks as a subclass of MINs. One of the authors of the previously mentioned paper also published [235], where MINs are used to establish active routers. Further publications describe multistage interconnection networks that connect a parallel computer [191] and MINs used to set up ATM switches [184].

The performance evaluation of wireless networks is broadly based [150, 174, 185, 190]. Some publications relate to handoffs in a cellular network, which is close to one of the applications of this book. For instance, the book deals with the spatial distribution of wireless networks and their performance evaluation using Markov chains [25]. Further publications evaluating performance in the case of handoffs and considering the influence of architectures are [12] (using Markov chains) and [132] (using Petri nets). Markov chains as a method to model a cellular system supporting traffic of multiple bandwidth requirements are also applied in [101, 131]. Some assumptions about the movement of mobile nodes are given in [29].

# 1.4 Term Definitions

The basic terms of this book are introduced below, before the following chapters will use them in the defined context. Unfortunately, terminology in this field is not unique. Thus, other books may define them differently.

# 1.4.1 Models and Performance Evaluation

The term "performance evaluation" covers all kinds of methods to determine system performance. Section 1.1 already enumerated and classified these methods as measurement, simulation, and mathematical methods. This book mainly concentrates on the last two items. A detailed description of them will be given in Chap. 3. The methods are applied to evaluate network architectures for parallel and distributed systems.

The performance to be determined is usually described by latency and throughput of the network or of a part of it. Latency defines the time between the initiation of a message transmission at the source and its complete receipt at the destination [51]. That means the latency is the sum of the time for communication overhead at the source, signal delay time, ratio of message length to bandwidth, and the time for communication overhead at the destination [163]. Investigating network architectures, the communication overheads at the source and destination are usually not of interest. Furthermore, the ratio of message length to bandwidth can be neglected if message units are very small. Then, the delay time becomes the only quantity to characterize the latency (e.g., [32, 244]), particularly if no direct connection between the source and the destination is established. Comparing several network architectures, the delay times are compared by global clock cycles rather than by absolute values of time units [51]. This book also characterizes network architectures by their delay times measured in clock cycles. The throughput of a network is defined as the amount of information delivered per time unit [51]. Again, this quantity can be determined related to absolute values of time units or to clock cycles, as practiced in the remaining part of this book. The throughput heavily depends on network size. Thus, the throughput is usually normalized by dividing it by the network size.

Simulation or mathematical methods for performance evaluation are applied by modeling the system in question. A model is an abstract or theoretical representation of this system. Many different models can be used to describe the system behavior. Often, a simplified system behavior is modeled to keep the model size reasonable.

# 1.4.2 Parallel System Architecture

A parallel system refers to a system that executes an action simultaneously with tightly coupled devices [194]. The devices support each other via the exchange of intermediate results received by performing a part of the action. If a device fails, the action usually cannot be completed, which especially corresponds to failed connections between the devices.

Tanenbaum [196] defines a parallel system (for instance, a multicomputer system) as a system that "(simultaneously) works on a single problem."

Parallel systems can be found in many areas. This book focuses on parallel systems related to computer science: devices (e.g., nodes of a computer system) are connected by a communication network and perform an action in close cooperation [1, 2, 115, 119, 167].

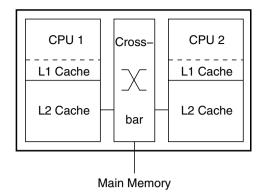

Multiplying matrices on a parallel computer system is a typical example. The parallel computer system consists of hundreds of processors. They are connected by a high-performance communication network, e.g., a crossbar or a hypercube (see Sect. 2.3). The matrix multiplication is divided into multiple independent scalar multiplications. Each processor performs a part of those scalar multiplications. The results are transferred to some of the processors and further evaluated there. If a processor fails (and no redundancy is available), some results are missing and the product of the matrices cannot be determined.

Parallel system architecture refers to overall features concerning the parallel system design. Its main issues are the structure and the behavior of the system.

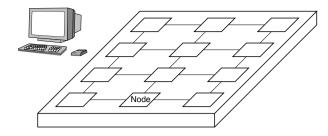

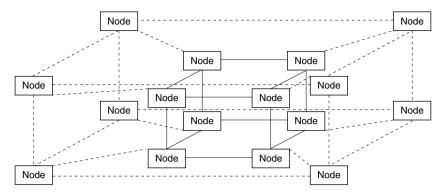

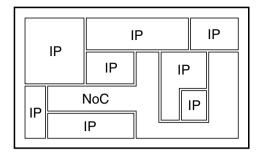

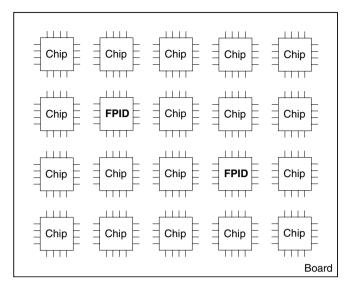

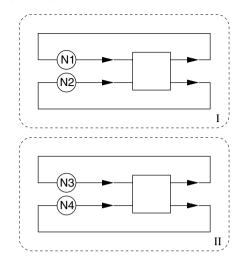

For instance, Fig. 1.1 roughly shows the architecture of a parallel computer system. The main elements of the system are the nodes. Usually, they consist of processors and some local node memory. The nodes are all close together, e.g., on a computer main board or on separate boards that are directly connected.

Tightly coupling the devices requires in general a structure of closely located devices: a parallel system is established in a limited area.

Fig. 1.1. Architecture of a parallel computer system

#### 1.4.3 Distributed System Architecture

A distributed system refers to a system that executes an action with loosely coupled devices [194]. Communication time between the devices only represents a small fraction of the entire execution time. Therefore, the devices need not to be highly meshed. They may be distributed in a wide area.

If a device fails, distinct tasks are no longer available. But all other devices proceed with their actions. Even if the connection between them fails, distinct tasks are no longer available but all devices remain in service as stand-alone devices.

As in case of parallel systems, this book only focuses on distributed systems related to computer science: devices (e.g., stand-alone computers) are connected by a communication network and perform an action in loose cooperation (by communicating every now and then).

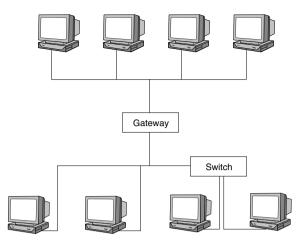

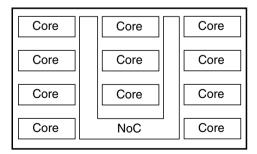

Distributed system architecture refers to all features concerning distributed system design. For instance, Fig. 1.2 roughly shows the architecture of a distributed computer system. It consists of several computers connected via a network. The computers commonly solve a task or can act as stand-alone machines. Even computers of distinct networks can work together if networks are connected (e.g., via a gateway or switch [6, 77]). Due to the networks, large distances may exist between computers of a distributed system [247].

Several definitions describe parallel systems as a subset of distributed systems. For instance, Tanenbaum [195, 196] defines a distributed system as "a set of independent computers that appear to the user as a single system." Discussing the hardware concept of such systems, he explicitly includes shared memory systems (multiprocessor systems) besides distributed memory systems (multicomputer systems).

In this book, parallel systems like shared memory systems are distinguished from distributed systems by their tight coupling via the memory: if a processor accesses (a part of) the memory that is located at a particular port, all other processors are blocked in the case of accessing the same (part of the) memory. As a result, communication time increases (if the delay until the data transfer between processor and memory starts is also included in the communication

Fig. 1.2. Architecture of a distributed computer system

time). Communication time represents in this context the time from a data request to the memory until the data is delivered to the requesting processor.

Nevertheless, there is a smooth transition between parallel and distributed systems. For instance, if the shared memory system consists of a shared memory with multiple ports or if each processor holds its own cache memory, the processors are no longer coupled as tightly as in the previous example.

Coulouris' definition [40] of a distributed system does not agree with Tanenbaum's. Shared memory systems (with common memory) are excluded from distributed systems. He defines a distributed system as "one in which components located at networked computers communicate and coordinate their actions only by passing messages." This means that only message-passing systems belong to the set of distributed systems.

Coulouris derives from his definition three main features of distributed systems: concurrency of components, lack of a global clock, and independent failures of components. The last two features particularly emphasize the character of loosely coupled devices in distributed systems. Systems synchronized by a global clock or in which failed components cause further failures must be called tightly coupled.

## 1.4.4 Network Architecture

Previous sections show that a major component of parallel and distributed systems is their network. It allows communication between parallel or distributed devices. Due to tightly coupled devices of parallel systems, messages that are exchanged in such systems should be received with only a short delay. To meet the demands of high network performance, the devices usually are located close together, avoiding large distances to be traveled by messages within the network. As a result, networks of parallel systems only cover a local area.

The network architecture describes the network topology and its physical realization by determining the kinds and parameters of the network elements in detail. The network topology only gives the structure of the connections between the nodes related to graph theory.

Devices of distributed systems may be spread over a large area, which means that a network linking the devices is also spread over a large area. The local parts of such a network are usually connected by switches. The switches often consist of similar architectures as networks for parallel systems [51, 184]. This book focuses on such architectures.

Distributed systems that include mobile devices need networks that deal with this additional issue. Such wireless networks are also a topic of this book. The performance and dynamic behavior of links between wireless devices and wired devices are the main focus. Distributed computer systems with mobile devices allow mobile computing, also called nomadic computing [94, 126]. Ubiquitous computing [68, 161, 228] overlaps with mobile computing: ubiquitous computing assumes many computing devices in the user's environment allowing ubiquitous computer access. Such computing devices may include mobile devices. Ubiquitous computing is also called pervasive computing.

In general, devices of a parallel or distributed system, which are connected via a network, are also called communication partners or nodes in this context, independently of whether they are mobile or fixed devices.

# **Characteristics of Network Architectures**

In comparing parallel and distributed systems, many characteristics surface that both systems have in common. This chapter introduces those characteristics. It concentrates on characteristics highlighted by the communication aspects of parallel and distributed systems. Due to coupled devices, both kinds of systems require a network between the devices allowing communication. Common characteristics concerning message transfer (switching techniques), network architectures, and network traffic patterns are described. Protocols and fault tolerance are not investigated in this book, and are thus not addressed.

# 2.1 Switching Techniques

A common task of parallel systems and distributed systems is their need for a communication system. It connects the devices (nodes) of the system and enables any required message exchange between them. The switching techniques [45, 163, 181] describe when and how message components are transferred along a network link. They are not in charge of determining the path that the message takes through the network. This job is performed by the routing algorithm and is not subject of this book. Only some routing basics related to particular network architectures are explained in Sects. 2.3 and 2.4.

# 2.1.1 Circuit Switching

The circuit switching technique [108] reserves a physical link between the sender (source node) and the receiver (destination node). Reservation is established by a control information (probe) between source and destination. Then, the physical link is reserved for the total transfer time. Therefore, network resources may heavily be wasted if the amount of transferred data per time unit (called data rate) is lower than the rate the link is able to deal

with. Furthermore, messages of other communication partners may not be exchanged due to these reserved links (message blocking).

On the other hand, after establishing a connection, no further signaling is needed during message transfer except for the releasing of the link at the end of the transfer. Thus, circuit switching performs well if messages are long.

At the hardware level, messages are usually divided into phits (physical units). A phit represents the smallest unit that can be transferred during a hardware clock cycle. Depending on the link width, a phit usually consists of at least one and up to 64 bits.

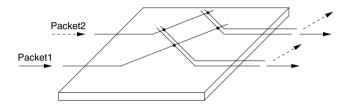

# 2.1.2 Packet Switching

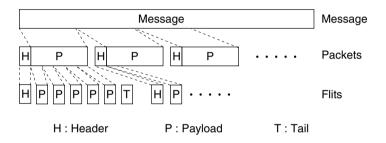

The packet switching technique divides a message into several packets. Packets consist of a header field and a payload field (Fig. 2.1, top). The header

Fig. 2.1. Dividing a message into packets and flits

contains the destination information. Further information may also be added, like packet length (if the packets are not of equal length), sender information, or any other switching information. The payload field contains message data. Packet switching has the advantage that packets can be stored (buffered) during their transfer within the network (e.g., at intermediate nodes that have to be passed) due to their limited size. This means packets can be forwarded within parts of the network and stored at their current position in the case of blocking. Blocking may arise due to occupied buffers and links of intermediate nodes. After blocking, forwarding of buffered packets can be resumed.

Logical links are introduced describing the message path through the network. The feature of storing packets allows multiple logical links to use the same physical links: the resources are better utilized.

Three kinds of packet switching techniques are distinguished: store-and-forward switching, cut-through switching, and wormhole switching.

#### Store-and-Forward Switching

In store-and-forward switching [49], packets are forwarded from the source node to the destination node while being buffered at each intermediate node. A node forwards a packet when the succeeding node is available. A move from one node to the next one is called a hop.

## **Cut-Through Switching**

In cut-through switching [91, 179, 209, 230], packets are forwarded from the source node to the destination node in a manner similar to store-and-forward switching. But packets are buffered at an intermediate node only if the succeeding node is not available. In other words, packets move through ("cut through") the network by passing intermediate nodes until they are blocked. On the hardware level, the phits are forwarded in a pipeline manner.

If blocking occurs, packets are buffered until the blocking is released: virtual cut-through switching blocks the packet until the last phit arrives at this buffer, while in partial cut-through switching, phits are already allowed to proceed even if not all phits have reached the buffer where the packet is blocked.

Due to less buffering, packets traverse a network much faster than in the case of store-and-forward switching if only few blockings occur. If blocking occurs at each intermediate node, cut-through switching performs like storeand-forward switching.

## Wormhole Switching

In wormhole switching [21, 87, 136, 139, 148], packets are further divided into logical units called flits (flow control units). All flits (Fig. 2.1, bottom) are of equal size (usually between one and eight bytes). The first flit contains the header information and reserves a link through the network while it is forwarded in a cut-through switching manner. The following flits contain the payload. The last flit (called tail) deallocates the link.

Each intermediate node has a buffer of flit size. As in the case of cutthrough switching, the header flit moves through the network by passing intermediate nodes until it is blocked. If blocking occurs, the header flit is buffered at the related intermediate node. All other flits belonging to the same packet are buffered at their current intermediate nodes.

Dividing packets into flits of equal size reduces buffer costs. Intermediate nodes only need buffers of the flit size. On the other hand, if flits are blocked and buffered, the packet is spread over a part of the network. Due to the reserved link between the header flit and the tail flit, such a packet blocks a part of the network.

# 2.2 Traffic Patterns

Besides switching techniques, parallel and distributed systems also show some other common characteristics concerning their network traffic patterns. A particular network traffic pattern results from the communication requests of the network nodes. The times at which messages are sent and their particular destinations determine the traffic of one node. Superposing the traffic of all nodes gives the traffic pattern of the network.

That means the network traffic patterns are defined by the distribution of messages in space as well as by their distribution in time.

# 2.2.1 Distribution in Space

The distribution of messages in space can be related to the varying message density in network areas. But it can also describe the varying number of nodes a message is destined to. Both aspects will be discussed here.

# Uniformity and Hot Spot

Ideally, the message density is uniformly distributed all over the network. Such a traffic pattern ensures an equal load on all communication links. This is particularly important if all links have equal capacity.

Therefore, uniform traffic allows the design of very regular network structures, simplifying the network design. Equal network components can be used independently of the particular network area that is considered. Furthermore, establishing mathematical models of the network becomes much easier due to the regular and symmetric structure and uniform traffic, as will be seen in Sect. 3.2.

On the other hand, tasks or devices may be asymmetrically distributed among the network nodes. That means nodes are not equal in either their hardware or their software. Then, messages are usually non-uniformly distributed in the network. For instance, if only one node owns a main memory to store a huge amount of data, all other nodes send their data to this memory: a very high load results on the link to the memory node. In such a scenario, this link is called a hot spot [5, 100, 110, 166], and it may become a bottleneck of the system. More generally, a hot spot is any device in a system that turns into a performance bottleneck due to high utilization.

# Multicast

The varying number of nodes a message is destined to also describes a distribution in space. Sending a message to multiple destination nodes is called multicast [151, 182, 192, 200, 207, 209, 212, 225, 241]. The term multicast includes the two particular cases of unicast and broadcast. Unicast denotes the process of sending a message to only a single destination node whereas broadcast represents the process of sending a message to all destination nodes of the network.

A multicast can be realized either by message replication before routing (MRBR) or by message replication while routing (MRWR) [74, 238]. In MRBR [239], a multicast message that is destined to i nodes is copied i times before it is routed through the network. Then, those i messages are treated as unicast messages, each of them sent to one of the required destinations. In MRWR [18], the multicast message is sent as one message into the network. It proceeds through the network until it reaches a node or switch from which no single way leads to all required destinations. There, the message is copied as many times as there are different ways to reach all desired destinations. Such nodes or switches may be passed several times.

# 2.2.2 Distribution in Time

The distribution of messages in time addresses the time-dependent variation of the traffic density.

## **Initial Transient Phase**

The simplest case gives a scenario in which the traffic density changes only for a limited time interval and then ends up in a steady state. The network is said to be in an initial transient phase during the time of traffic change.

For instance, such a scenario arises if an idle network is connected to nodes that are sending messages at a constant rate. Depending on the network size and the rate, the network needs some time until it is filled with messages and remains in a steady state with regard to the quantity of messages in the network.

## **Basic Functions of Time**

The shape of time-dependent traffic in networks can be described by functions of time. Such a function of time that represents a single message in the network is also called signal in telecommunications. Signals that show a very simple shape are said to be basic signals. Table 2.1 introduces some basic signals. Symbol t denotes the time. Replacing t by  $t - t_0$  allows a time shift of the function by time  $t_0$ . Replacing t by  $\frac{t}{T}$  stretches the function by the constant T.

Usually, time-dependent traffic [204] in networks consists of a superposition of many signals sent from many source nodes. Particularly, the shape of such a superposition describes the distribution of messages in time (time-dependent variation of the traffic density).

Many distributions in time that show specific behavior are distinguished. Two of them, which result in an often observed traffic density shape, are addressed below: bursty traffic and multifractal traffic.

| Signal      | Description                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------|

| Sinus       | $s(t) = \sin(2\pi t)$                                                                                         |

| Gauss       | $s(t) = e^{-\pi t^2}$                                                                                         |

| Heaviside   | $\varepsilon(t) = \begin{cases} 0 & :  t < 0 \\ 1 & :  t \ge 0 \end{cases}$                                   |

| Rectangular | $\operatorname{rect}(t) = \begin{cases} 1 & : &  t  < \frac{1}{2} \\ 0 & : &  t  \ge \frac{1}{2} \end{cases}$ |

| Dirac       | $\delta(t) = \lim_{T_0 \to \infty} \frac{1}{T_0} \operatorname{rect}\left(\frac{t}{T_0}\right)$               |

Table 2.1. Basic signals

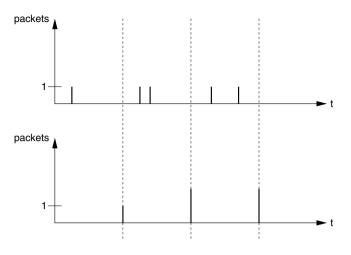

# **Bursty Traffic**

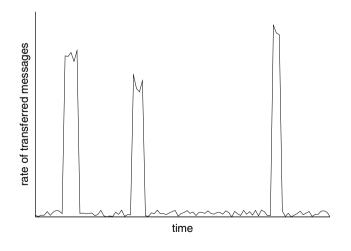

A special kind of time-dependent traffic is called bursty traffic [58, 205]. Bursts denote a high amount of transferred messages in a very short time. Bursty traffic consists of bursts separated by a longer period of fewer messages. Figure 2.2 gives an example. In parallel and distributed systems, bursts may be caused by transferring large files, large databases, large program code, and so on.

Fig. 2.2. Bursty traffic

## Multifractal Traffic

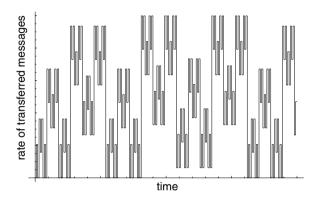

To define multifractal traffic [24, 28, 52, 215], self-similar traffic is introduced first. Self-similar traffic is defined as a traffic pattern that is invariant against changes in scale or size [116, 121, 122, 186, 232]. If a part of the self-similar traffic is cut out and magnified, it will show the same structure and behavior as the non-magnified original traffic.

An approximation of a self-similar traffic is depicted in Fig. 2.3. It is a

Fig. 2.3. Approximation of self-similar traffic

kind of a rectangular function. If a part of this function is cut out and magnified, this function again shows the same structure. This can be performed for several steps (time scalings). This self-similarity arises because the function of Fig. 2.3 is built by superposing periodical rectangle functions of different frequencies. The different frequencies represent different time scale factors.

Figure 2.3 does not really represent self-similar traffic because cutting out and magnifying the function for a few time scalings yields a similar structure, but the similarity stops if scaling is continued.

Self-similarity can easily be defined if discrete time traffic is assumed. For instance, this is true for clocked systems. A time discrete signal x(t) is said to be self-similar with parameter  $\beta$  ( $0 < \beta < 1$ ) if, for all  $m \in \mathbb{N} \setminus \{0\}$ ,

$$\operatorname{Var}(x^{(m)}) = \frac{\operatorname{Var}(x)}{m^{\beta}} \quad \text{and} \tag{2.1}$$

$$\rho_{x^{(m)}}(t) = \rho_x(t) \tag{2.2}$$

hold, where Var denotes the variance,  $\rho$  the autocorrelation, and

$$x^{(m)}(\tau) = \frac{1}{m} \sum_{t=\tau m - (m-1)}^{\tau m} x(t)$$

(2.3)

describes the average over m values of the original signal. Section 3.1.1 deals with the calculation of the variance and the autocorrelation.

The parameter  $\beta$  indicates the self-similarity. It is related to the Hurst parameter H which gives the degree of long-range dependence:

$$H = 1 - \frac{\beta}{2}.\tag{2.4}$$

A value of  $H \leq 0.5$  ( $\beta \geq 1$ ) expresses the lack of self-similarity. The closer H is to 1, the greater the self-similarity. H = 1 means  $\beta = 0$ , and results in

$$\operatorname{Var}(x^{(m)}) = \operatorname{Var}(x). \tag{2.5}$$

If  $\beta$  is not constant for all m, but constant with value  $\hat{\beta}$  for small m, and with a slight change for larger m, such traffic is called multifractal.

The definition of self-similarity for continuous time traffic emerges from an extension of above theory, and can be found in [186].

# Interarrival Time Distribution

The above sections describe the temporal behavior of traffic density in several ways. When modeling parallel and distributed systems, the behavior in time of the traffic is often stochastically described by the distribution of the time passing by until an event occurs. Such an event may be the random arrival of a new packet at a communication network. Then, this distribution is called the interarrival time distribution of the new packets. Waiting times, service times, and so on are also described by the same distributions.

The distribution function A(t) denotes the probability that the event under consideration occurred in the interval [0, t]. This function is also called the cumulative distribution function (CDF). Its derivative

$$a(t) = \frac{dA(t)}{dt} \tag{2.6}$$

is the probability density function (pdf).

One of the most important distributions is the exponential distribution. Its cumulative distribution function and probability density function are given, respectively, by

$$A(t) = 1 - e^{-\lambda t} \quad \text{and} \tag{2.7}$$

$$a(t) = \lambda e^{-\lambda t},\tag{2.8}$$

where  $\lambda$  represents the mean arrival rate. If service times are described,  $\lambda$  is replaced by  $\mu$ . The memoryless property of the exponential distribution is often used (see Sect. 3.2.1). It says that the probability of the occurrence of the investigated event in interval [0, t] is equal to the probability of its occurrence in interval  $[\tau, t + \tau]$  if it did not take place until time  $\tau$ .

The Erlang-k distribution describes the sum of k exponentially distributed phases with mean rate  $k\lambda$ . The CDF and pdf result in

$$A(t) = 1 - e^{-k\lambda t} \cdot \sum_{i=0}^{k-1} \frac{(k\lambda t)^i}{i!}$$

and (2.9)

$$a(t) = \frac{(k\lambda)^k \cdot t^{k-1} \cdot e^{-k\lambda t}}{(k-1)!},$$

(2.10)

with  $k \in \mathbb{N}$ . A generalization of this distribution is obtained if the restriction on k to be a natural number is relaxed. Such a distribution is called gamma distribution, where k is replaced by  $\alpha$  (with  $\alpha > 0$ ):

$$A(t) = \int_0^t \frac{\alpha \lambda \cdot (\alpha \lambda \tau)^{\alpha - 1}}{\Gamma(\alpha)} \cdot e^{-\alpha \lambda \tau} d\tau.$$

(2.11)

$\Gamma(\alpha)$  is defined by  $\Gamma(\alpha) = \int_0^\infty \tau^{\alpha-1} e^{-\lambda} d\tau$ . The Erlang-*k* distribution results from the gamma distribution for a positive integer  $\alpha = k$ .

The hyperexponential distribution describes the choice between k exponentially distributed phases with mean rates  $\lambda_i$ . The CDF and pdf are

$$A(t) = \sum_{\substack{i=1\\k}}^{k} q_i \left(1 - e^{-\lambda_i t}\right) = 1 - \sum_{\substack{i=1\\k}}^{k} q_i e^{-\lambda_i t} \quad \text{and}$$

(2.12)

$$a(t) = \sum_{i=1}^{\kappa} q_i \lambda_i e^{-\lambda_i t}, \qquad (2.13)$$

where  $q_i$  represents the probability that the *i*th phase is chosen. Thus,  $\sum_{i=1}^{k} q_i = 1$  holds.

To describe system failures, the Weibull distribution is often applied. Its CDF and pdf are

$$A(t) = 1 - e^{-(\lambda t)^{\alpha}}$$

and (2.14)

$$a(t) = \alpha \lambda^{\alpha} t^{\alpha - 1} e^{-(\lambda t)^{\alpha}}, \qquad (2.15)$$

where  $\alpha$  represents the shape parameter with  $\alpha > 0$ .

A distribution describing non-stochastic behavior is given by the deterministic distribution. The investigated event is assumed to take place at time  $t_0$ . Thus, no stochastic behavior is involved. The cumulative distribution function and probability density function result in

$$A(t) = \begin{cases} 0 & : \quad t < t_0 \\ 1 & : \quad t \ge t_0 \end{cases} \quad \text{and} \tag{2.16}$$

$$a(t) = \begin{cases} 1 & : \quad t = t_0 \\ 0 & : \quad \text{otherwise.} \end{cases}$$

(2.17)

To model multifractal traffic as presented in Sect. 2.2.2, the Pareto distribution is often proposed to describe the related interarrival times. It belongs to the group of heavy tailed distributions where the tail of the distribution is hyperbolic (i.e.  $t \to \infty$ ). The CDF and pdf of the Pareto distribution are given by

$$A(t) = 1 - \left(\frac{b}{t}\right)^{\alpha} \quad \text{and} \tag{2.18}$$

$$a(t) = \alpha \cdot \frac{b^{\alpha}}{t^{\alpha+1}},\tag{2.19}$$

with  $0 < \alpha < 2$ . It is defined over the interval  $t \ge b$ .

A distribution where each value in an interval  $[b_l, b_r]$  will be chosen with equal probability is called uniform distribution:

$$A(t) = \begin{cases} 0 & : t < b_l \\ \frac{t - b_l}{b_r - b_l} & : b_l \le t \le b_r \\ 1 & : t > b_r \end{cases}$$

and (2.20)

$$a(t) = \begin{cases} \frac{1}{b_r - b_l} & : \quad b_l \le t \le b_r \\ 0 & : \quad \text{otherwise} \end{cases}$$

(2.21)

represent the its CDF and pdf.

Errors or values given by a sum of many other values are often distributed according to the normal distribution (also called Gaussian distribution). Its probability density function is given by

$$a(t) = \frac{1}{\sqrt{2\pi\sigma^2}} e^{-\frac{(t-\mu)^2}{2\sigma^2}},$$

(2.22)

with the location parameter  $\mu$  representing the mean and with the scale parameter  $\sigma$  representing the square root of the variance (see Sect. 3.1). No closed-form cumulative distribution function for the normal distribution exists.

Many further distributions are known, e.g., Cox distribution, double exponential distribution (also called Laplace distribution), Student's *t*-distribution, lognormal distribution, and beta distribution, among others[107].

All previously mentioned distributions are continuous. Interarrival times of discrete time systems are modeled by discrete distributions. They are characterized by their cumulative distribution functions and their probability mass functions. The probability mass function p(t) denotes the probability with which an arrival occurs at discrete time t.

Many discrete distributions exist. For instance, the geometric distribution offers the memoryless property as the exponential distribution does in the case of continuous time. The cumulative distribution function and the probability mass function are defined by

$$A(t) = 1 - (1 - p)^{t+1}$$

and (2.23)

$$p(t) = p \cdot (1-p)^t,$$

(2.24)

with  $t \in \mathbb{N}$  represents the *t*-th time step and (1-p) gives the probability that no arrival occurred in a time step.

The discrete uniform distribution describes several possible times  $t_i$  at which an arrival may occur. The cumulative distribution function and the probability mass function are given by

$$A(t) = \begin{cases} 0 : t < t_l \\ \frac{t - t_l + 1}{t_r - t_l + 1} : t \in \{t_l = t_0, t_1, \dots, t_r\} \\ 1 : t > t_r \end{cases} \text{ and } (2.25)$$

$$p(t) = \begin{cases} \frac{1}{t_r - t_l + 1} & : \quad t \in \{t_l = t_0, t_1, \dots, t_r\} \\ 0 & : \quad \text{otherwise.} \end{cases}$$

(2.26)

The number of arrivals in an interval when the arrivals occur at a constant rate are often described by the Poisson distribution with

$$A(t) = \frac{e^{-\lambda}\lambda^t}{t!} \quad \text{and} \tag{2.27}$$

$$p(t) = e^{-\lambda} \sum_{i=0}^{t} \frac{\lambda^{i}}{i!},$$

(2.28)

where  $t \in \mathbb{N}$ .

Other discrete distributions include the Bernoulli distribution, the binomial distribution, and the negative binomial distribution, among others [107].

# 2.3 Wired Network Architectures

The most important and critical step in designing a communication system for a parallel or distributed system is to choose the network architecture. The architecture is given by the network topology, the buffer sizes, the buffer positions, and so on.

The chosen architecture must fulfill all requirements given by the amount and shape of the expected network traffic, the number of communication partners, and the distance between them. Network architectures are classified as wired or wireless. In this section, it is focused on wired network architectures, while the next section will deal with wireless network architectures. Network architectures for on-chip communication, with their particular characteristics, are introduced in Sect. 2.5.

Many wired network architectures have been proposed [6, 51, 77, 119, 133, 186, 195]. Some of them are briefly discussed below.

# 2.3.1 Basic Classifications

In general, wired networks are categorized as direct or indirect. Direct networks are also called static networks. They consist of a limited number of fixed point-to-point links between some communication partners (nodes). Messages are transferred from a source node (sender) to a destination node (receiver) via intermediate nodes. There are no further switches to change links. For instance, a mesh (Sect. 2.3.3) belongs to this group of networks. The most important characteristic of direct networks is their node degree: the number of links of a node to neighboring nodes.

Indirect networks are also called dynamic networks. They consist of many switches to dynamically change links between nodes. No intermediate nodes are involved in transferring a message from a source node to a destination node. For instance, a crossbar (Sect. 2.3.9) belongs to this group of networks. The most important characteristic of indirect networks is their number of stages: the number of switches of a connection.

The switches in indirect networks may themselves consist of dynamic networks. For instance, smaller crossbars may realize the switches in multistage interconnection networks (Sect. 2.3.10). The nodes of direct networks usually also contain such switches. They connect all inputs and outputs of the node and its core. Thus, direct networks as well as indirect networks may reveal a hierarchical structure.

The way several pairs of nodes communicate in a network without interference is called multiplexing. In wired networks, two kinds of multiplexing are mainly used: multiplexing in space and multiplexing in time.

Space division multiplexing (SDM) separates communication channels of different sender-receiver pairs by space. That means different pairs of nodes use different wires that are not connected to each other. Switches between the wires ensure that nodes of sender-receiver pairs may change if desired. The large quantity of wires needed for a large number of communication pairs is the main disadvantage of SDM.

Time division multiplexing (TDM) allows a sender-receiver pair to use a wire for a certain amount of time. Then, another sender-receiver pair can access this wire for a certain amount of time, and so on. Thus, only a single wire is needed. But TDM suffers from the drawback that all nodes must be synchronized. Only if all nodes deal with exactly the same time, are they able to send or receive in the desired time slice and not interfere with any other node.

Space division multiplexing and time division multiplexing may also be combined. Pure SDM is used in fully connected network architectures where each node is connected to every other node. Pure TDM is used in a single bus architecture.

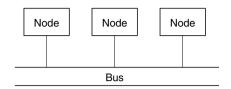

#### 2.3.2 Bus

The most common network architecture to connect few nodes is a bus (Fig. 2.4). Each node is connected to the bus. The source node (called master)

Fig. 2.4. Bus architecture

initiates the communication by allocating the bus. It transmits the destination node's address and the message via the bus. All nodes listen to the bus and compare this address with their own. An address match identifies the destination node (called slave), which reads the message. Finally, the bus is deallocated.

Due to the concept of a single common bus, time division multiplexing must be applied and only one sender is allowed to transfer a message at a given time. That is why the bus becomes a bottleneck in a communication system consisting of a large number of nodes.

To overcome this problem, some systems use several busses to combine time division multiplexing and space division multiplexing. Each bus connects only a part of the nodes. All busses are linked to a switching fabric which couples the whole system. Switching fabric architectures are discussed in Sect. 2.3.11.

Busses profit from their simple hardware setup and from their simple routing.

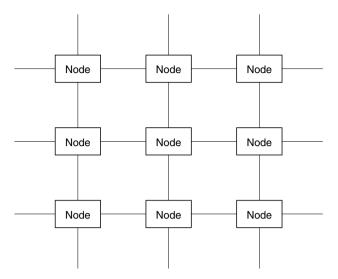

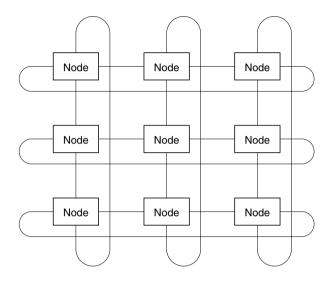

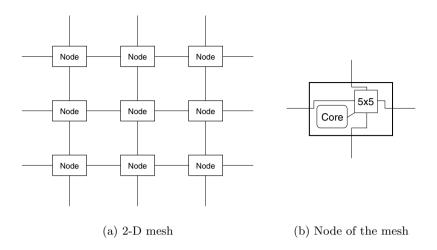

#### 2.3.3 Mesh

A popular static network architecture of parallel computers is a mesh [48]. In such an architecture, the nodes are located at the crosspoints of the mesh. Three kinds of meshes are distinguished: one-dimensional meshes (also called chains), two-dimensional meshes (2-D meshes, grids), and three-dimensional meshes (3-D meshes). Figure 2.5 shows a 2-D mesh.

Each node is connected to its two nearest neighbors in each dimension. For instance, four bidirectional links handle all communication of a node of a 2-D mesh. The number of links per node does not change if additional nodes are added to the mesh. Therefore, a mesh offers very good scalability. Additionally, it is of low cost, because a mesh network consists of fewer links per node than most other architectures (crossbars and their hierarchies as an exception are presented later).

Fig. 2.5. 2-D mesh architecture

Their blocking behavior reveals one of the most important disadvantages of meshes. Usually, messages pass several nodes and links before they reach their destination. As a result, links are demanded by many connections using the same link; blocking occurs. Blocking can be reduced if communication is mainly local, e.g., if a task to solve differential equations or finite element methods is spread over nodes. Then, messages are exchanged only between nodes located close together.

Messages are mostly transferred by packet switching, leading to simple routing, another advantage of meshes. For instance, the packet header includes the destination information as  $\Delta x$  and  $\Delta y$  (in the two-dimensional case) representing the destination node distance in the x direction (horizontal) and the y direction (vertical), respectively. Packets may then be forwarded in the x direction first. The sign of  $\Delta x$  determines whether the positive or the negative direction must be chosen. Each intermediate node decrements/increments  $\Delta x$ . If  $\Delta x = 0$  is reached, the packet is forwarded in the y direction in the same manner.  $\Delta y = 0$  means that the destination is reached.

This algorithm is called XY routing. Other algorithms are, for instance, the West-First, North-Last, and Negative-First routing, where particular turns are forbidden.

Many variations on the above scheme are known. Forwarding in x direction and y direction may be merged to get alternative paths through the mesh. Partially forwarding in the wrong direction may help avoid blockings or faulty links.

#### 2.3.4 Torus

An extension of the mesh architecture is given by the torus. It is a mesh network where all boundary nodes show additional links to their corresponding boundary node at the opposite boundary. Figure 2.6 depicts a two-dimensional torus (2-D torus). Three-dimensional tori (3-D tori) also exist. Higher dimen-

Fig. 2.6. 2-D torus architecture

sions are possible, too. The communication network of many parallel computer systems consists of a 3-D torus.

A torus is a static network, like a mesh. Due to their similar structure, a torus reveals the same advantages and drawbacks as a mesh. A slight benefit compared to a mesh is the shorter average distance between two communicating nodes in a torus. The additional links at the boundary avoid long distances between opposite nodes.

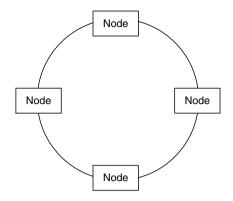

## 2.3.5 Ring

Another static network is called ring. In such an architecture, each node is connected to exactly two other nodes, one on each side, leading to an overall structure of a closed loop (Fig. 2.7). Having only two neighboring nodes keeps the amount of interfaces per node very small.

Messages are sent to the ring and usually circle in a common direction from node to node. Each node checks whether it is the receiver. A ring network often realized is the token ring. There, a token synchronizes the nodes' access to the network. The token circles on the ring to signal the status of the network.

Fig. 2.7. Ring architecture

To send a message, nodes must wait to receive the token. If it is marked as "empty," the message can be sent, and the token marking is changed to "occupied." Nodes that receive this token now are not allowed to send. After the message circles around once, it is removed and the token is marked as "empty" again.

The main drawback is that the entire network is affected if any link fails. Doubling each link reduces the problem. Such an architecture is called dual ring.

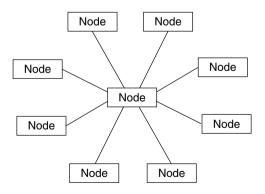

## 2.3.6 Star

The star network describes a static architecture where all nodes are connected to a central node (Fig. 2.8). Thus, all nodes (except the central one) can only communicate to the others via the central node. That is why the central node may become a bottleneck of a system that consists of many nodes.

Fig. 2.8. Star network architecture

On the other hand, only two hops are needed to reach any of the other nodes. If the central node is sender or receiver, a single hop realizes a communication.

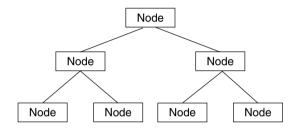

### 2.3.7 Tree

In the static architecture of a tree network, all nodes are arranged as a tree: a root node is connected to descendant nodes. These nodes are again connected to descendant nodes, and so on. Nodes with no further descendant nodes are called leafs.

If the structure of the tree is such that all nodes (except the leafs) are connected to a fixed number k of descendants, the network architecture is called a k-ary tree. For instance, Fig. 2.9 shows a binary tree. This tree is

Fig. 2.9. Binary tree network architecture

also called balanced because all leaf nodes have the same distance to the root node.

If the nodes of a tree are arranged such that communication mainly takes place between nodes that are located in the same (minimum) subtree, connections consist of only few hops.

On the other hand, if any node in the left half of the tree communicates with any node in the right half, the communication is established via the root node. Therefore, the root node acts as a bottleneck of the network.

An alternative structure, named fat tree [114], overcomes this problem: Nodes are placed only at the leafs of the tree. The nodes at the tree branches are replaced by switches, and the capacity of the connections is increased by k at each stage from the leafs to the root. A dynamic network architecture results. It is topologically equivalent to a bidirectional multistage interconnection network, described in detail in Sect. 2.3.10.

#### 2.3.8 Hypercube

A further static network architecture is given by a hypercube [168]. The nodes of the hypercube also represent the nodes of the network. As an example,

Fig. 2.10. 4-D hypercube architecture

Figure 2.10 shows a four-dimensional hypercube (4-D hypercube). It is established by a 3-D hypercube (solid lines) where each node is connected to an additional node of another 3-D hypercube (dashed lines) forming a 4-D hypercube.

Hypercubes can be built of any dimension d, connecting  $N = 2^d$  nodes. Nevertheless, an existing hypercube cannot be enlarged to a higher dimension unless there are unused ports at the nodes.

Concerning the blocking behavior, equal problems arise as for meshes. But blocking occurs less frequently because messages use less links in average from source node to destination node. At most, d hops are needed to reach a destination.

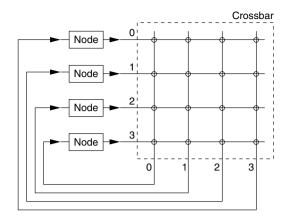

## 2.3.9 Crossbar

Crossbars [59, 98, 152, 176, 214, 237, 243, 245] are dynamic networks consisting of a switch matrix. This switch matrix ensures that each network input can be connected to each network output via exactly one switch: A connection consists of only a single hop. Figure 2.11 shows a  $4 \times 4$  crossbar, which consists of four inputs and four outputs. This means that the crossbar connects four nodes. Alternative graphical representations of crossbars are depicted in Fig. 2.12. The right part of the figure gives the simplest way of representation, and is mainly used.

The switches are located at the crosspoints of the horizontal and vertical lines. Each switch corresponds to a specific input-output pair. The inputs and outputs are connected to the related source nodes (senders) and destination nodes (receivers).

Crossbars of c inputs and c outputs produce  $c^2$  switches/crosspoints. This means that the crossbars are scalable, but the complexity increases quadratically; the main drawback of crossbars. Hierarchically connected crossbars, e.g., multistage interconnection networks (Sect. 2.3.10), avoid this drawback.

Fig. 2.11. Crossbar architecture

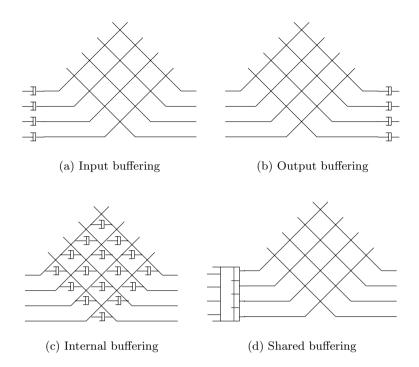

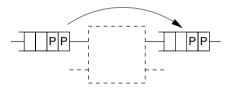

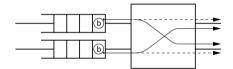

If messages are forwarded by packet switching, buffers can be inserted to prevent packet loss in the case of conflicts for resources [30]. Usually, firstin first-out (FIFO) buffers are used. Several buffer locations are appropriate: buffers at crossbar inputs, buffers at crossbar outputs, internal buffers, and shared buffers [250].

Figure 2.13(a) shows a crossbar architecture, including buffers at crossbar inputs (input buffering) [230]. Input buffering suffers from head-of-line (HOL) blocking, for instance, if the first position of all buffers is occupied by packets that are destined to the same crossbar output. Then, all packets except one are blocked, and most parts of the crossbar remain idle. Even if the second buffer position contains a packet destined to another output, the crossbar mainly remains idle because this packet cannot pass the blocked packet.

Buffers at the outputs (output buffering) [123, 249] overcome this problem (Fig. 2.13(b)). The major drawback of such a buffer location is the high packet transfer rate of the crossbar that is needed, for instance, if all c crossbar inputs

Fig. 2.12. Alternative crossbar representations

Fig. 2.13. Crossbar buffer locations

receive a packet destined to the same output. Then, the transfer rate of the crossbar must be c times as high as the input rate at the crossbar.

Internal buffers overcome both previously mentioned problems. Figure 2.13(c) depicts such a buffer scheme. But there are also drawbacks to this architecture: a much higher number of FIFO buffers  $(c^2)$  is needed. This means that hardware cost is increased.

A completely different buffering scheme is given by shared buffers [177, 210]. Shared buffers can be located at crossbar inputs (Fig. 2.13(d)), crossbar outputs, or internally. A common pool of buffer space is available. Each input/output allocates buffer space as required.

The drawback of such a buffering scheme emerges from the higher control cost: the buffer must manage where to store which packet. Internal queues have to be used to keep the transfer order of the packets.

## 2.3.10 Multistage Interconnection Network

To overcome the drawbacks of crossbars, multistage interconnection networks (MIN) [1, 55, 71, 87, 99, 104, 119, 140, 179, 235, 242] are frequently proposed

to connect the nodes of parallel systems or to establish switching fabrics (Sect. 2.3.11) connecting the nodes of distributed systems.

Such architectures were already used to design telephone switches in the 1960s. At that time, Beneš [13, 14] investigated MINs operating in circuit switching mode and established a mathematical description of their behavior. Nowadays, buffers are inserted [250] and packet switching is applied to MIN architectures that are part of computer networks.

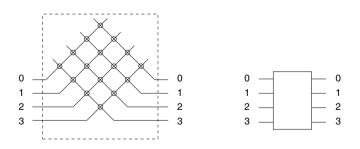

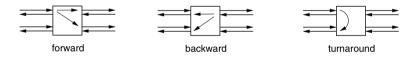

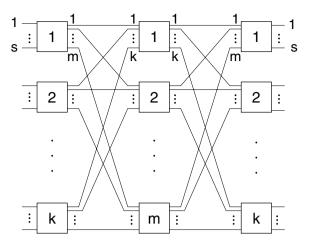

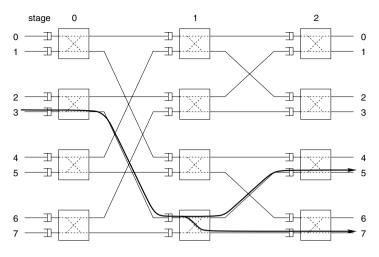

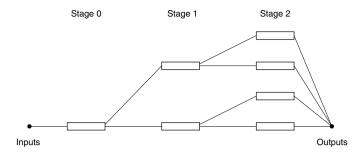

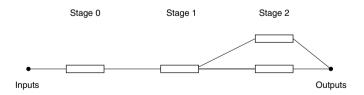

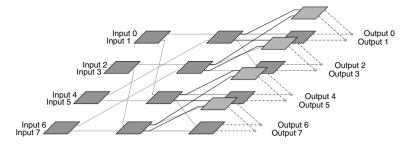

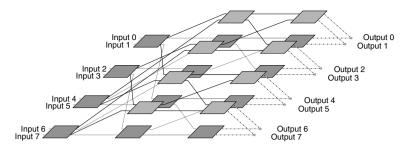

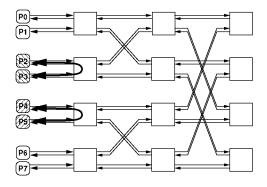

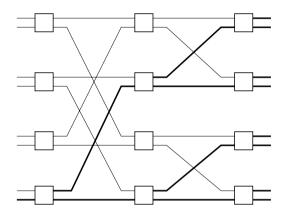

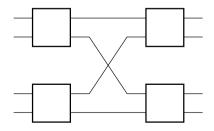

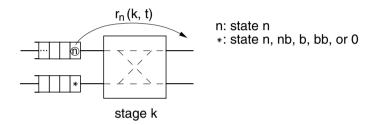

MINs are dynamic networks based on switching elements (SEs) [84]. The most common approach to realize SEs are crossbars. SEs are arranged in stages and connected by interstage links. The link structure and number of SEs characterizes the MIN. Several MIN architectures exist.

#### MIN with Banyan Property

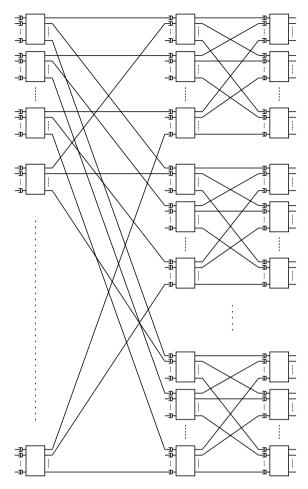

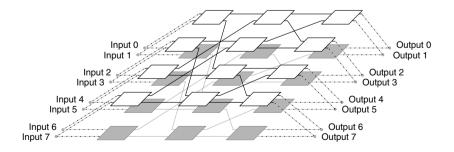

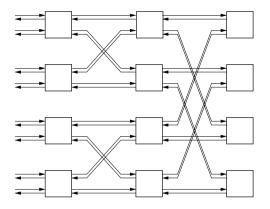

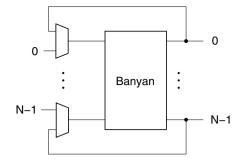

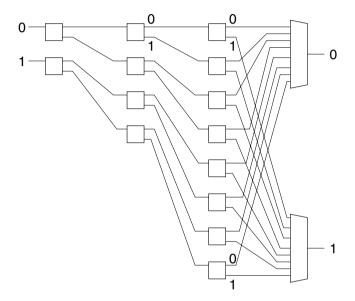

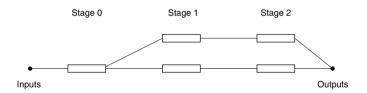

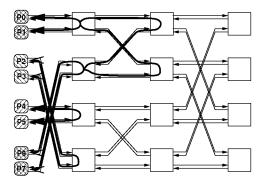

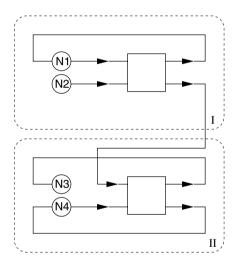

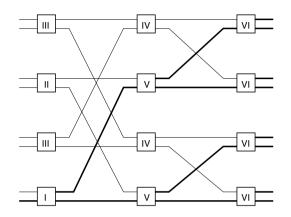

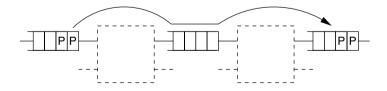

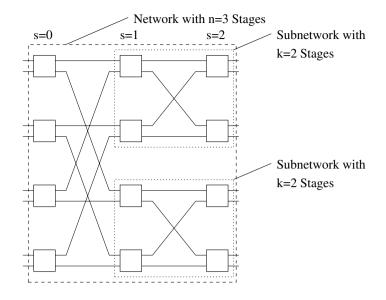

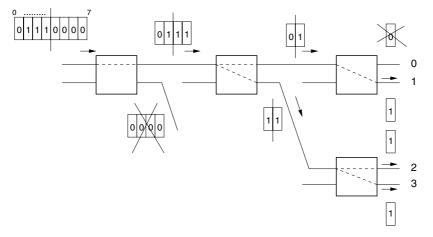

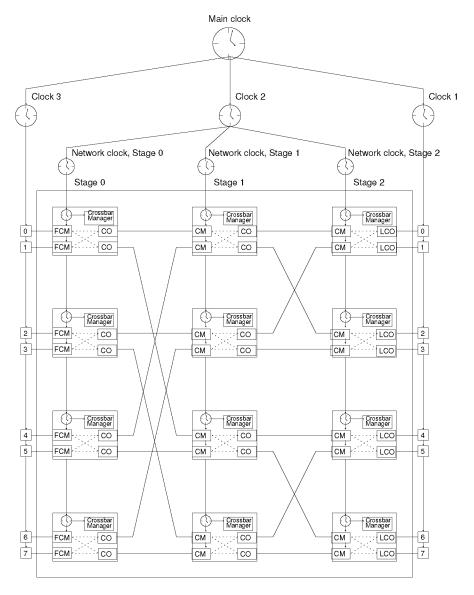

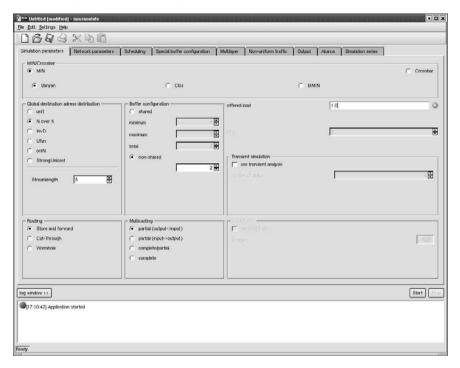

Multistage interconnection networks with the banyan property [33, 49, 85, 103, 179] are networks where a unique path from an input to an output exists. Such MINs of size  $N \times N$  (N inputs and N outputs) consist of  $c \times c$  switching elements (SEs of c inputs and c outputs) [32, 156, 216] with  $n = \log_c N$  stages (Fig. 2.14).

To achieve synchronously operating switches, the network is internally clocked [246]. This network clock cycle consists of as many hardware clock cycles as are needed to completely forward all phits of a packet for one stage.

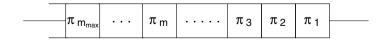

At each stage k ( $0 \le k \le n-1$ ), there is a FIFO buffer of size  $m_{max}(k)$  in front of each SE input [50, 142, 206, 244]. Of course, output buffering, internal buffering, or shared buffering are also possible. The packets are forwarded by store-and-forward switching, cut-through switching, or wormhole switching from one stage to its succeeding one.

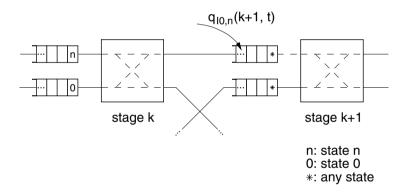

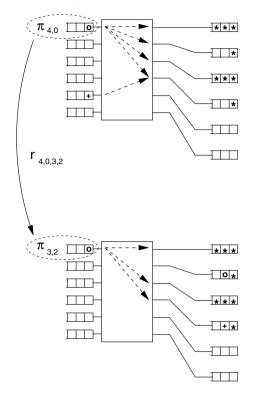

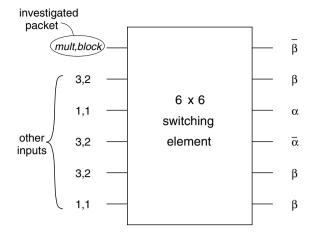

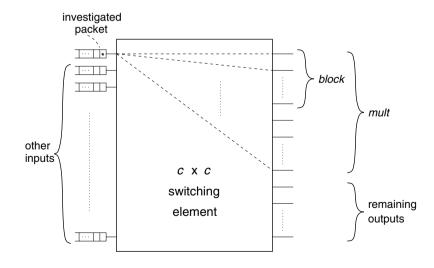

Packets that are destined to full buffers can be handled by dropping those packets [240] or by applying the backpressure mechanism. The backpressure mechanism keeps packets in their current stage until the required buffer becomes available again. This means that no packets are lost within the network. Local and global backpressure are distinguished. Local backpressure observes only the destination buffer at the next stage: the packet at stage k is sent if space at stage k + 1 is available. Global backpressure acquires additional information about packet flows: the packet at stage k is sent even if no space at stage k + 1 is available, but will become available by the time the packet is received. Such a situation may arise if a packet leaves stage k + 1 at the same clock cycle.

The network shown also belongs to the class of delta networks. This means that it is a banyan network where all packets can use the same routing tag to reach a certain network output independently of the input at which they enter the network. Rectangle delta networks additionally demand square SEs (i.e., equal number of SE inputs and outputs), shown in Fig. 2.14. This network also belongs to the class of regular delta networks (i.e., equal size of all SEs)

Fig. 2.14. Three-stage delta network consisting of  $c \times c$  SEs

and bidelta networks (i.e., delta property for input-to-output direction and output-to-input direction).

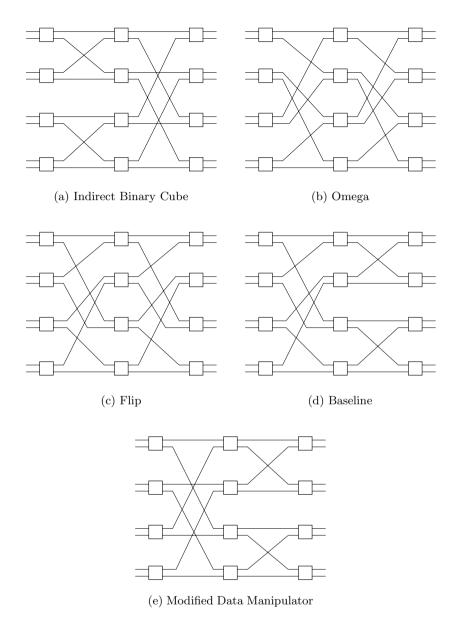

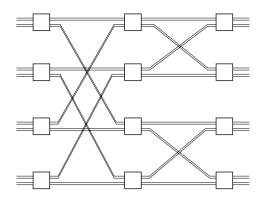

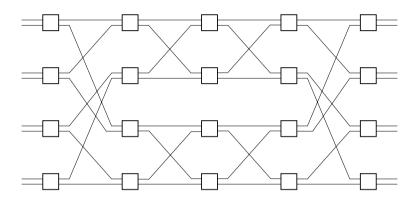

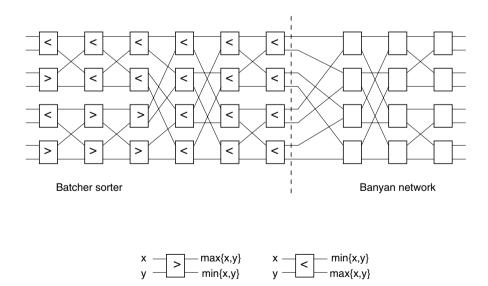

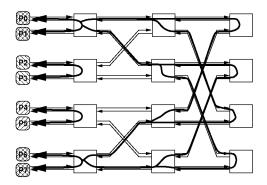

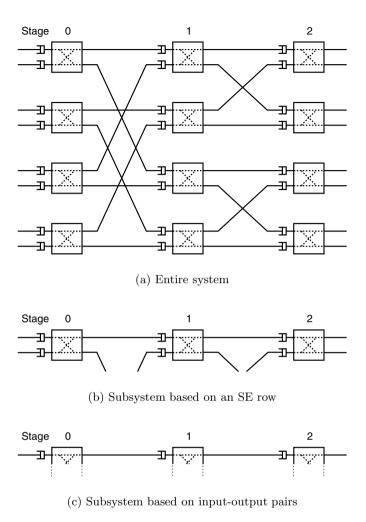

Various bidelta network architectures consisting of  $2 \times 2$  SEs are depicted in Fig. 2.15. In the literature [102, 103], they are referred to as Omega, Flip, Baseline, Indirect Binary Cube (IBC), and Modified Data Manipulator (MDM). Their interstage connections distinguish them. For instance, the interstage connections of the Modified Data Manipulator are established by numbering the SEs at each stage k. Numbers are coded to the base of c, starting with 0. This means that each SE is numbered by a (n - 1)-digit number  $\nu_{n-1}\nu_{n-2}\ldots\nu_2\nu_1$ , where  $0 \leq \nu_i \leq c-1$  and  $1 \leq i \leq n-1$ . Then, SE  $\nu_{n-1}\nu_{n-2}\ldots\nu_2\nu_1$  at stage k is connected to c SEs at stage k + 1 that are numbered  $\nu_{n-1}\ldots\nu_{n-k} \diamond \nu_{n-k-2}\ldots\nu_1$ , where  $\diamond$  equals all values from 0 to

Fig. 2.15. Bidelta networks consisting of  $2 \times 2$  SEs

c-1. The rules concerning the interstage connections of all architectures of Fig. 2.15 are given in Table 2.2.

| Bidelta network | SEs at stage $k+1$                                       |

|-----------------|----------------------------------------------------------|

| MDM             | $\nu_{n-1}\ldots\nu_{n-k}\diamond\nu_{n-k-2}\ldots\nu_1$ |

| Omega           | $\nu_{n-2} \dots \nu_1 \diamond$                         |

| Flip            | $\diamond  u_{n-1} \dots  u_2$                           |

| Baseline        | $\nu_{n-1}\ldots\nu_{n-k}\diamond\nu_{n-k-1}\ldots\nu_2$ |

| IBC             | $ \nu_{n-1} \dots \nu_{k+2} \diamond \nu_k \dots \nu_1 $ |

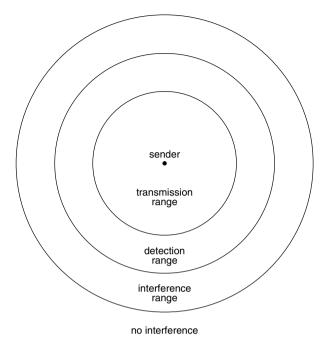

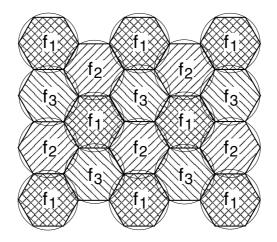

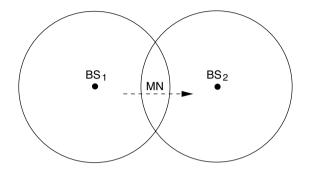

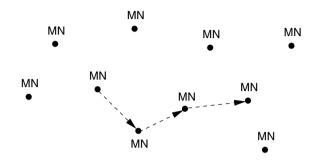

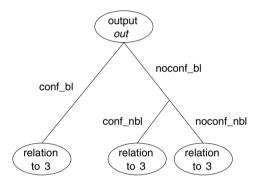

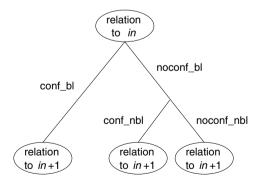

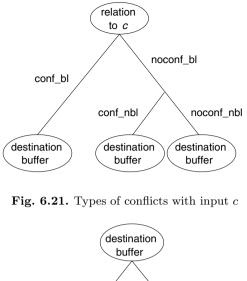

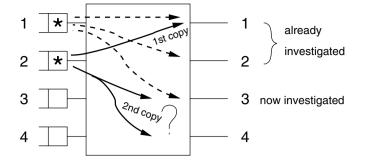

Table 2.2. Interstage connections